网站添加新闻栏怎么做seo推广方式是什么呢

在 FPGA 实现 FIR 滤波器时,最常用的是直接型结构,简单方便,在实现直接型结构时,可以选择串行结构/并行结构/分布式结构。

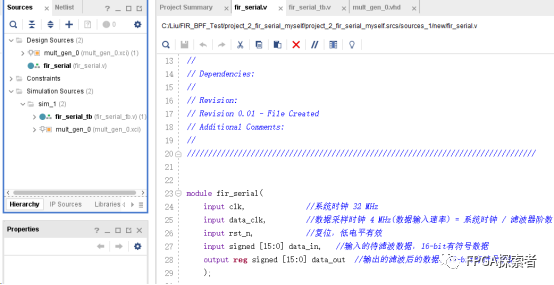

串行结构即串行实现 FIR 滤波器的乘累加操作,数据的处理速度较慢。N 阶串行 FIR 滤波器,数据的输入速率 = 系统处理时钟速率 / 滤波器长度(N+1),本例使用 7 阶串行,系统时钟 32 MHz,这样数据的输入速率(也是采样速率)为4 MHz;

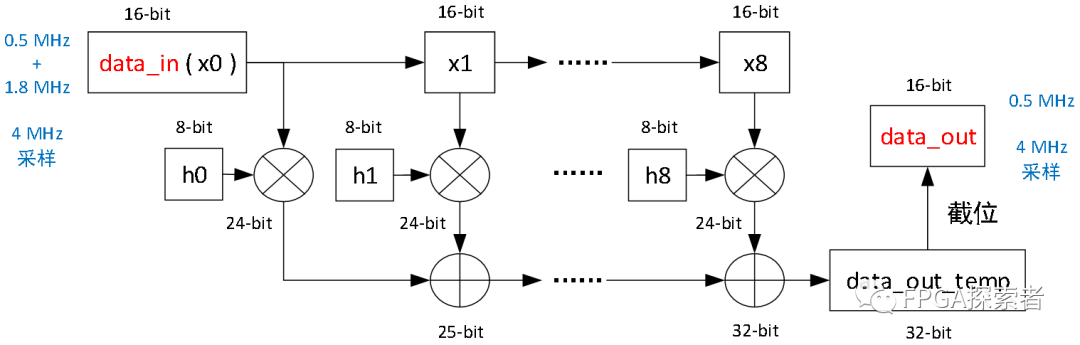

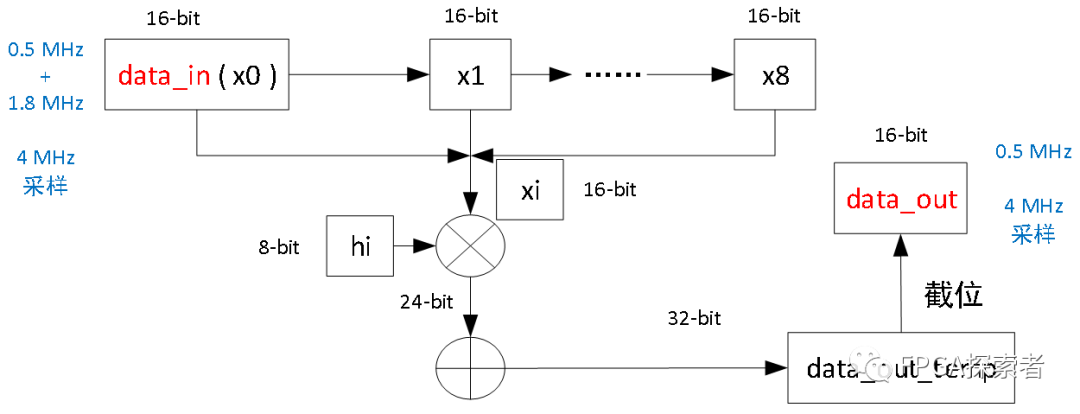

7 阶串行 FIR 滤波器结构框图如下图所示,只使用一个乘法器,按照输入顺序依次串行使用该乘法器,

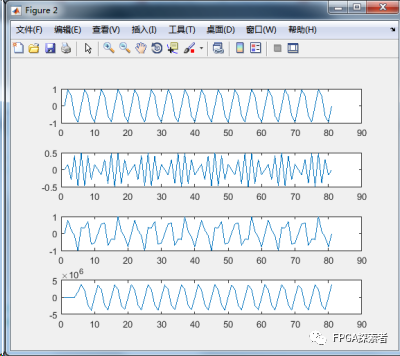

输入信号为 0.5 MHz 叠加 1.8 MHz 信号,采样时钟为 4 MHz(系统处理时钟频率 / 滤波器阶数)16-bit量化;

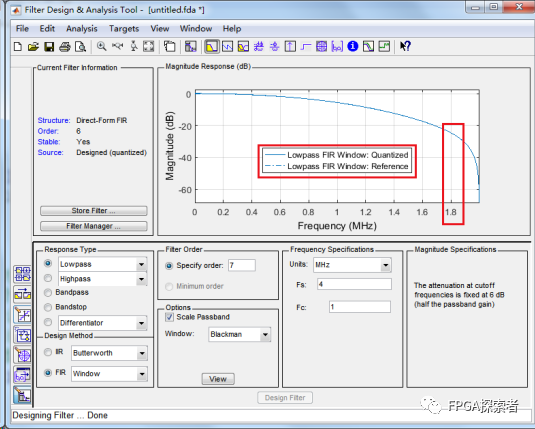

滤波器系数 8-bit量化,4 MHz抽样,低通滤波器(Low Pass Filter,LPF),截止频率 1 MHz,窗函数设计,Blackman窗;

输出信号为 0.5 MHz信号,16-bit截位;

1. 新建工程和文件

(1) 新建 Verilog 文件,输入信号 16-bit,输出信号 16-bit,复位 rst_n 低电平进行复位;

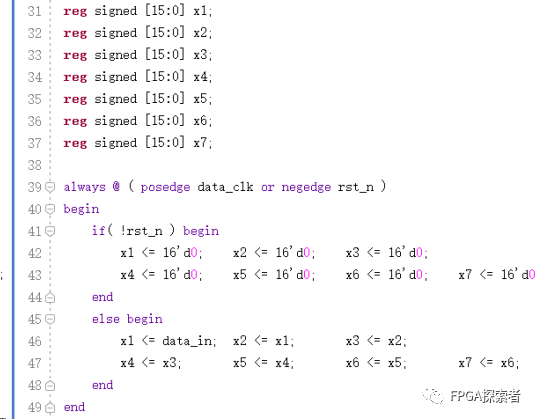

(2) 定义 x0 ~ x8 并赋值;

在数据输入时钟 data_clk 的上升沿进行数据的移位操作,低电平复位时初始化 x0 ~ x8 均为 0,rst_n 为高电平时进行数据的移位操作(注意看前面的框图);

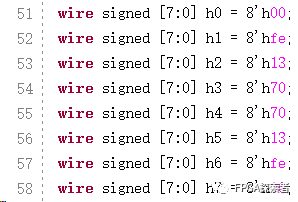

(3) 获取滤波器系数 h0 ~ h8;

按照 第一讲 的方式使用 matlab 的 fdatool 工具箱设计 FIR 低通滤波器,设置为系数 8-bit 量化,采样时钟 4 MHz(4MHz = 32MHz / 8),截止频率设为 1 MHz(截止频率越低,滤波效果越好,此处使用的阶数只有 7 阶,所以把截止频率再设低一些);

在 1.8 MHz 信号衰减接近 -30 dB,幅度是原来的几百分之一,实线和虚线几乎完全重叠,表明 8-bit 的滤波器系数量化基本不影响滤波效果。

量化后导出参数,可以直接用 .coe 文件导出备用,导出后 matlab 也会自动打开系数文件,用 Verilog 语言的常数定义参数 h0 ~ h7(注意指定为有符号数);

(4) 加权求和进行滤波

FIR 滤波器的输出是输入信号不同延时阶段的数据和滤波器系数的卷积(乘累加操作),也相当于每个输入延时数据有不同的权值,进行加权和;

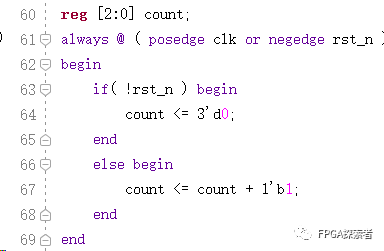

使用一个计数器 count 对系统处理时钟 clk 来计数,共计 8 个数(0 ~ 7),每个数对应处理一个乘法;

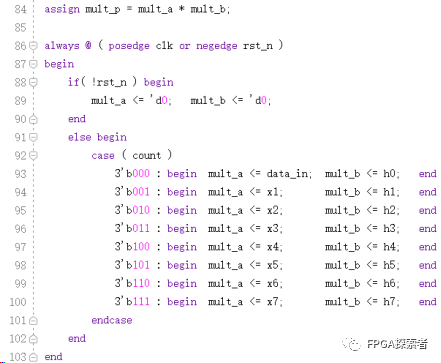

定义乘数a :reg signed [15:0] mult_a;

定义乘数b :reg signed [7:0] mult_b;

定义积 :wire signed [23:0] mult_p;

每个计数值对应相应的乘法器输入,这样共计 8 个 clk 时钟完成 8 次乘法操作,但是只是用了 1 个乘法器(在不同时间用的),节省了资源,但是速度较慢;

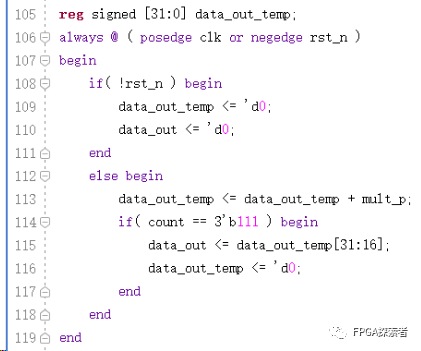

对乘法输出累加,在累加了 8 个值后,输出累加值并把原来的累加值清零;

2. 使用 matlab 产生仿真信号

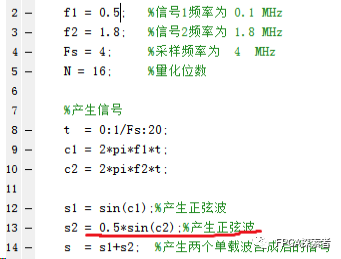

参数:抽样频率 Fs = 4 MHz,信号 f1 = 0.5 MHz,信号 f2 = 1.8 MHz,具体参见第三讲matlab与FPGA数字滤波器设计(3)—— Matlab 与 Vivado 联合仿真 FIR 滤波器;

红线部分前面乘0.5,让高频噪声信号的幅度小一些,这样滤波效果比较明显,不然 7 阶 FIR 滤波器的效果比较差;

3. 编写仿真文件testbench

(1)例化模块;

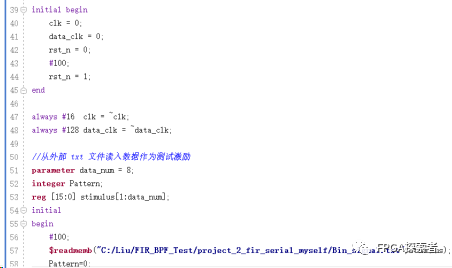

(2)写 initial 块,初始化时钟、复位等;

(3)写 always 块,给出时钟翻转等;

(4)读写 .txt 文件,将 matlab 写好的 .txt 的数据赋给输入,把输出数据写入 .txt 文件给 matlab 分析;

具体见第三讲;

matlab与FPGA数字滤波器设计(3)—— Matlab 与 Vivado 联合仿真 FIR 滤波器

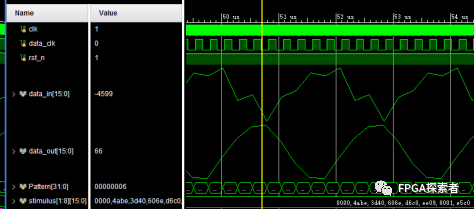

4. 仿真

阶数太少,滤波效果一般;

Matlab仿真,分别是 f1、f2、f1+f2、滤波后的数据;

由于串行滤波器的速度限制,当处理频率较高的数据时,要求的系统时钟就需要更高,所以要想办法进行优化;

(1)观察 FIR 滤波器的系数可以发现,系数是对称的,这也是 FIR 滤波器对称结构的特性,对于本例来说,h0与h7一样,h1与h6一样…,则对于 data_in * h0 + x7*h7 可以简化为 (data_in + x7) * h0,先计算对称的加法,再计算乘法,A*B+A*B = (A+A)*B,这样对于一个 7 阶的 FIR滤波器(8个滤波器系数),只需要计算 4 次乘法,在系统时钟和阶数不变的情况下,数据的输入速率可以由原来的 4 MHz提高到 8 MHz;或者说在输入速率和系统时钟不变的情况下,可以把阶数从 7 阶(8个系数)做到 15 阶(16个系数),使得滤波效果更好;

(2)上述利用对称性能够提高一定的速度,但是在阶数较高是仍然面临系统时钟需求较高的问题, 此时可以利用“用资源换速度”的思想,并行处理,并加入流水线,这样消耗了更多的资源,但是提高了运行速度;

matlab与FPGA数字滤波器设计(4)—— Vivado DDS 与 FIR IP核设计 FIR 数字滤波器系统

matlab与FPGA数字滤波器设计(3)—— Matlab 与 Vivado 联合仿真 FIR 滤波器

matlab与FPGA数字滤波器设计(2)——Vivado调用IP核设计FIR滤波器

matlab与FPGA数字滤波器设计(1)——通过matlab的fdatool工具箱设计FIR数字滤波器

欢迎关注:FPGA探索者