dede中英文网站切换守游网络推广平台

设计过程

1.写出真值表,使用卡诺图化简表达式(每一位输出都需要单独写,注意加上无关项)

2.看哪些可以作为一个整体,再次化简的。

3.画出电路图。

Map

1.将所有的门转换成非门+或非/非门+与非的组合。(替换and和or)

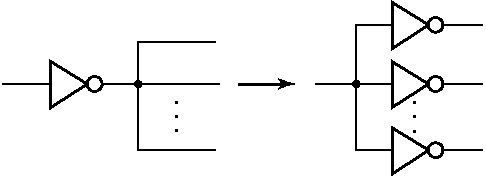

2.如果总线内每一根都有非门,则将总线内的非门移到总线外

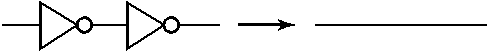

3.将两个非门去掉

组合逻辑

使能函数

如果,EN=1则使能,F输出X,否则输出0/1

Decoder(译码器)

将一个二进制转化为一个输出

1-2译码器

2-4译码器

可以由小译码器组成大译码器

3-8译码器只需要将1-2译码器的2个输出和2-4译码器的4个输出分布与起来。

如果将逻辑表达式写成SOP的形式,那么将最小项系数对应的解码器的输出或起来就是表达式本身

Demultiplexer(多路复用器)

用译码器控制输出的为输入的2的n次中的某一个值。

因此m-多路复用器有m个选择输入,2的m次个信号输入,一个输出

对于真值表来说:对于一个输出,只需要将真值表中的输入按照顺序排列,再将输出的值赋值给多路复用器对应的输入即可。这样每一个输入都会选择一个输入对应的值输出。

| Gray | Binary |

| 0 0 0 | 0 0 0 |

| 0 0 1 | 1 1 1 |

| 0 1 0 | 0 1 1 |

| 0 1 1 | 1 0 0 |

| 1 0 0 | 0 0 1 |

| 1 0 1 | 1 1 0 |

| 1 1 0 | 0 1 0 |

| 1 1 1 | 1 0 1 |

对应的输出为:

如果给的多路复用器刚好少一位时,当前两位相同时,看输出和第三位的关系。然后进行赋值。

如果输出为1,则赋值为1,输出为0,则赋值为0,否则赋值为C或者C'

算术模块

half-adder半加器

不能计算之前的进位。

对于1位加法 X+Y:

加法值为:

加法进位为:

full-adder全加器

计算带进位的加法

对于1位加法 X+Y和进位Z:

4位全加器

Carry Lookahead Adder(CLA超前进位加法器)

由于进位需要从最低位开始传输,因此可能出现传输延迟。

可以发现进位只和每一次的加数以及初始的进位有关,因此可以直接计算出进位

可以通过以上四式进行迭代产生,直接计算最后的进位结果

Unsigned Subtraction(无符号减法)

1‘s complement(反码):直接每位取反

2'scomplement(补码):每位取反后加1

对于减法:M-N:

结果为M加上N的补码。如果M>N会产生一个进位,如果M<N不会产生进位。

为了得到负的结果,将M-N补码的结果求补码,再加上负号(相当于0-(-|M-N|))

比如:0101 0100b-0100 0011b

将后一个求补码:1011 1101b

与前一个相加:1 0001 0001b,产生进位,说明原来的结果是正的

比如:0100 0011b-0101 0100b

将后一个求补码:1010 1100b

与前一个相加:1110 1111b,未产生进位,说明原来的结果是负的

如果想求绝对值,则求补码:0001 0001b,结果为-0001 0001b

Signed Integer(符号数)

最高位为1,说明是负数。最高位为0,说明是正数。

Signed-Magnitude :除最高位以外的数,代表一个符号数的绝对值。

Signed-Complement:符号数补码,有1和2两种形式

如果是符号数正数,则两种补码都是本身。

如果符号数负数,

1'sign complement: 符号位不变,Sign-Mag求反码

2'sign complement:符号位不变,sign-Mag求反码+1,如果导致进位则说明不存在

Signed-Magnitude Arithmetic(符号数运算)

如果两个操作数和操作符的符号位奇偶校验为0,则将它们的Sign-Mag相加,最后结果和第一个操作数符号相同。

负号符号位相当于1,正号符号位相当于0。

如果3个的符号位奇偶校验位1,则从第一个减去第二个,如果发生借位,则取结果的补码,符号为第一个操作数的符号

Signed-Complement Arithmetic

加法:将符号位和Sign-Mag都参加加法运算,但是忽略符号位的进位

如果两个操作数的符号位相同但是结果的符号位不同,则发生了溢出

减法:取包括符号位的补码,然后相加。

Adder/Subtractor

如果S=1,则结果是取B的补码和A相加,否则取B和A相加